Жедел есте сақтау құрылғыларының интегралды микросхемалары

Жедел есте сақтау құрылғыларының интегралды микросхемалары ақпаратты жазу, сақтау және оқуға арналған және ақпаратты таңдауы еркін есте сақтау құрылғыларының тобына жатады. Олар үш түрге бөлінеді: өте жедел регистрлік, жедел динамикалық және жедел статикалық.

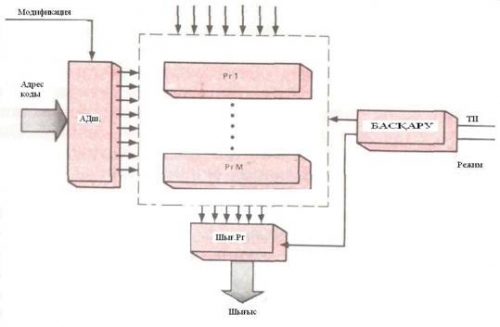

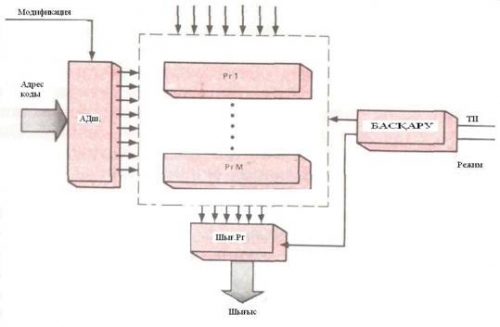

Жоғары тез әрекет етушілікті қамтамасыз ету үшін есептеуіш жүйеге өте жедел ЕСҚ (ӨЖЕСҚ) қосады, оның тез әрекет етушілігі процессордың тез әрекет етушілігіне тең немесе одан артық. Мұндай ӨЖЕСҚ-да ақпарат D- немесе JK-триггерлерден қалыптасқан регистрлерде сақталады. Мұндай регистрлік ӨЖЕСҚ-ның құрылымдық схемасы суретте келтірілген. Схема n разрядты параллелді М регистрлерді (Prj) қамтиды. Олардың әрқайсысына адрес дешифраторына (АДш) келіп түскен адрес бойынша жүгінуге болады. Адрес коды процессордың арқылы «Модификация» сигналының көмегімен өзгертіле алады. Жұмыс режимі «Режим» кірісіне келіп түскен кернеу деңгейімен анықталады. Тактілік импульс (ТИ) кірістегі ақпараттың таңдалған регистрге жазылуын немесе шығыс регистрі (Рг Шығ) арқылы ақпараттың оқылуын қамтамасыз етеді.

Динамикалық ЖЕСҚ интегралды схемалары өзінің күйін тек белгілі бір уақыт аралығында сақтайтын, сондықтан периодтық қалпына келтіріуді немесе регенерацияны талап ететін есте сақтау элементінің негізінде құрылады. Динамикалық ЖЕСҚ-ның есте сақтау элементі ретінде конденсатор қызмет етеді. Онда ақпарат зарядтың болуы немесе болмауы түрінде сақталады. Кеміп қалу нәтижесінде конденсатордағы заряд бірте-бірте азаяды. Зарядты қалпына келтіру үшін конденсаторды әлсін-әлсін қорек көзіне қосады.

Динамикалық ЖЕСҚ-дағы есте сақтаушы ұяшық бір транзистор немесе конденсатордан жасалады, нәтижесінде мұндай ұяшық алатын аудан салыстымалы аз, ол динамикалық ЖЕСҚ микросхемасының кристалына милионнан астам есте сақтаушы ұяшықтарды «буып-түюге» мүмкіндік береді. Динамикалық ЖЕСҚ кемшілігі ақпаратты регенрециялау схемасын қосу қажеттілігі болып табылады, бірақ бұл кемшілік ЖЕСҚ басқа типтеріне қарағанда ақпарат сыйымдылығының үлкендігімен өтеледі.

Статикалық ЖЕСҚ интегралды схемалары 4-8 транзисторлар негізінде құрылған триггерлік есте сақтау ұяшықтарының негізінде жасалады. Статикалық ЖЕСҚ артықшылығы жоғары тез әрекетушілік, қосымша ақпаратты регенерациялау схемаларын енгізу қажеттілігінің жоқтығы болып табылады. Статикалық ЖЕСҚ кемшілігі жүгіну режимінде де, ақпаратты сақтау режимінде де үнемі қорек көзінен ток тұтынуы болып табылады.

Аударма Ә.К.Бөрібаева

Жоғары тез әрекет етушілікті қамтамасыз ету үшін есептеуіш жүйеге өте жедел ЕСҚ (ӨЖЕСҚ) қосады, оның тез әрекет етушілігі процессордың тез әрекет етушілігіне тең немесе одан артық. Мұндай ӨЖЕСҚ-да ақпарат D- немесе JK-триггерлерден қалыптасқан регистрлерде сақталады. Мұндай регистрлік ӨЖЕСҚ-ның құрылымдық схемасы суретте келтірілген. Схема n разрядты параллелді М регистрлерді (Prj) қамтиды. Олардың әрқайсысына адрес дешифраторына (АДш) келіп түскен адрес бойынша жүгінуге болады. Адрес коды процессордың арқылы «Модификация» сигналының көмегімен өзгертіле алады. Жұмыс режимі «Режим» кірісіне келіп түскен кернеу деңгейімен анықталады. Тактілік импульс (ТИ) кірістегі ақпараттың таңдалған регистрге жазылуын немесе шығыс регистрі (Рг Шығ) арқылы ақпараттың оқылуын қамтамасыз етеді.

Динамикалық ЖЕСҚ интегралды схемалары өзінің күйін тек белгілі бір уақыт аралығында сақтайтын, сондықтан периодтық қалпына келтіріуді немесе регенерацияны талап ететін есте сақтау элементінің негізінде құрылады. Динамикалық ЖЕСҚ-ның есте сақтау элементі ретінде конденсатор қызмет етеді. Онда ақпарат зарядтың болуы немесе болмауы түрінде сақталады. Кеміп қалу нәтижесінде конденсатордағы заряд бірте-бірте азаяды. Зарядты қалпына келтіру үшін конденсаторды әлсін-әлсін қорек көзіне қосады.

Динамикалық ЖЕСҚ-дағы есте сақтаушы ұяшық бір транзистор немесе конденсатордан жасалады, нәтижесінде мұндай ұяшық алатын аудан салыстымалы аз, ол динамикалық ЖЕСҚ микросхемасының кристалына милионнан астам есте сақтаушы ұяшықтарды «буып-түюге» мүмкіндік береді. Динамикалық ЖЕСҚ кемшілігі ақпаратты регенрециялау схемасын қосу қажеттілігі болып табылады, бірақ бұл кемшілік ЖЕСҚ басқа типтеріне қарағанда ақпарат сыйымдылығының үлкендігімен өтеледі.

Статикалық ЖЕСҚ интегралды схемалары 4-8 транзисторлар негізінде құрылған триггерлік есте сақтау ұяшықтарының негізінде жасалады. Статикалық ЖЕСҚ артықшылығы жоғары тез әрекетушілік, қосымша ақпаратты регенерациялау схемаларын енгізу қажеттілігінің жоқтығы болып табылады. Статикалық ЖЕСҚ кемшілігі жүгіну режимінде де, ақпаратты сақтау режимінде де үнемі қорек көзінен ток тұтынуы болып табылады.

Аударма Ә.К.Бөрібаева

мә, рахатыңа пайдалан: